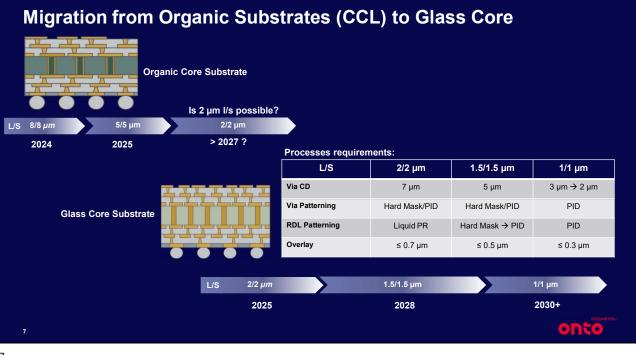

## The Challenges for Organic & Glass core Substrates As Advanced Packaging RDL Approaches 2 µm L/S And Beyond

#### MAY 3rd, 2024

Keith Best Director, Product Marketing, Lithography

### **Disclaimer**

Onto Innovation's statements regarding its plans, directions, and intent are subject to change or withdrawal without notice at Onto's sole discretion.

Information regarding potential future products is intended to outline our general product direction and it should not be relied on in making a purchasing decision.

The information mentioned regarding potential future products is not a commitment, promise, or legal obligation to deliver any material, code or functionality. Information about potential future products may not be incorporated into any contract.

The development, release, and timing of any future features or functionality described for our products remains at our sole discretion.

Performance is based on measurements and projections using standard Onto benchmarks in a controlled environment. The actual throughput or performance that any user will experience will vary depending upon many factors. Therefore, no assurance can be given that an individual user will achieve results similar to those stated here.

## Onto Connected Panel Solution Accelerates New Product Ramp

### Onto Connected Panel Solution Meets current and next generation adv IC

- Meets current and next generation adv IC substrate development requirements Accelerates time to solution in yield

- optimization Facilitates collaboration across adv IC

- substrate ecosystem

### Value to Our Customers

- Increases manufacturing productivity

- Reduces overall investments to reach yield entitlement

- Enables shorter time for new product introduction

- Accelerates technology development

7

## Glass Core 2 $\mu m$ l/s and Beyond Challenges

|                      |                                     | Challenges                                                     |

|----------------------|-------------------------------------|----------------------------------------------------------------|

| Glass Core Substrate | Substrate Core                      | Thin glass panel handling                                      |

|                      |                                     | TGV CDU (top, bottom, waist) and defectivity (cracks, residue) |

|                      |                                     | TGV plating uniformity                                         |

|                      |                                     | Cavity for embedded dies                                       |

|                      | Hard Mask and PID for<br>Patterning | Hard Mask - Material selection and selectivity to ABF          |

|                      |                                     | PID – Material selection and reliability                       |

|                      | Cu Seed Deposition                  | Adhesion, surface roughness and thickness control              |

|                      | Cu Via/Trace Plating                | Plated copper roughness, Cu seed removal                       |

|                      | Embedded<br>Components              | Embedded die shift                                             |

|                      |                                     |                                                                |

| 2/2 μm               | 1.5/1.5 μm                          | 1/1 μm                                                         |

| 2025                 | 2028                                | 2030+                                                          |

|                      |                                     |                                                                |

|                      |                                     | 0                                                              |

# Organic Substrate (CCL) 2 µm l/s Challenges

#### Challenges

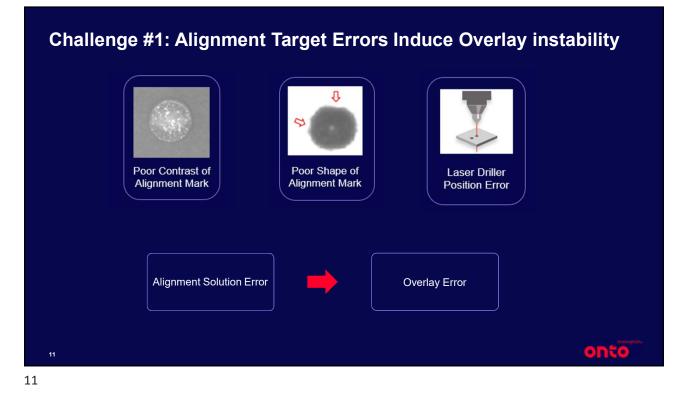

- 1. Overlay Via to RDL Pad

- 2. Dielectric Lamination Uniformity and Defectivity Control

- 3. RDL 2D/3D Metrology and Defectivity Control

- 4. Via CD and Defectivity Control

- 5. Seed Layer Deposition Thickness Control

- 6. Via/RDL Plating Uniformity and Defectivity

- 7. Embedded Die Placement

#### To reach 2 µm l/s:

- Production Overlay, RDL to Via (12  $\mu$ m  $\rightarrow$  < 2  $\mu$ m)

- Build up film, Via CD (30  $\mu$ m  $\rightarrow$  <10  $\mu$ m),

- · Process ramp must have acceptable yield

#### 9

# Organic Substrate (CCL) 2 µm l/s Challenges

#### Challenges

#### 1. Overlay - Via to RDL Pad

- 2. Dielectric Lamination Uniformity and Defectivity Control

- 3. RDL 2D/3D Metrology and Defectivity Control

- 4. Via CD and Defectivity Control

- 5. Seed Layer Deposition Thickness Control

- 6. Via/RDL Plating Uniformity and Defectivity

- 7. Embedded Die Placement

#### To reach 2 µm l/s:

- Production Overlay, RDL to Via (12  $\mu$ m  $\rightarrow$  < 2  $\mu$ m)

- Build up film, Via CD (30  $\mu$ m  $\rightarrow$  <10  $\mu$ m),

- · Process ramp must have acceptable yield

onto

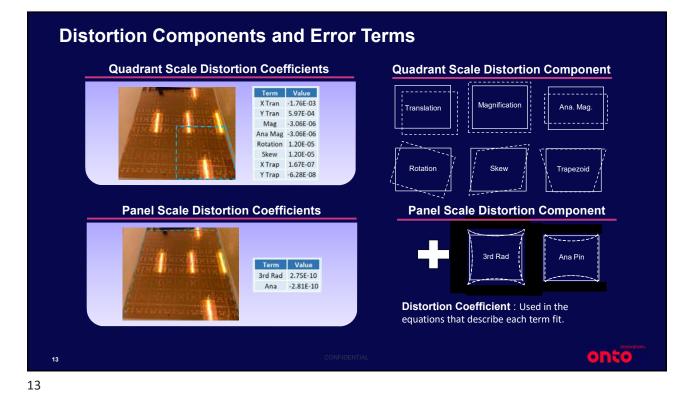

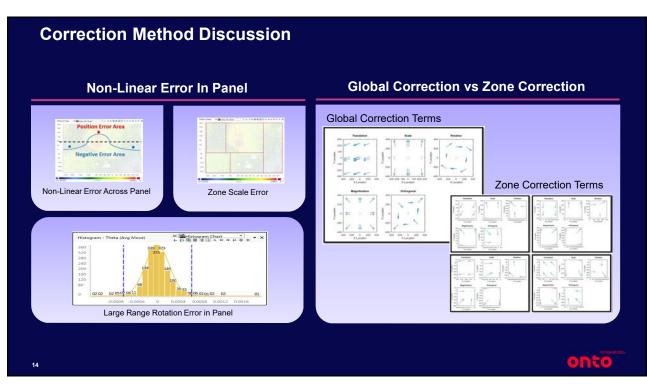

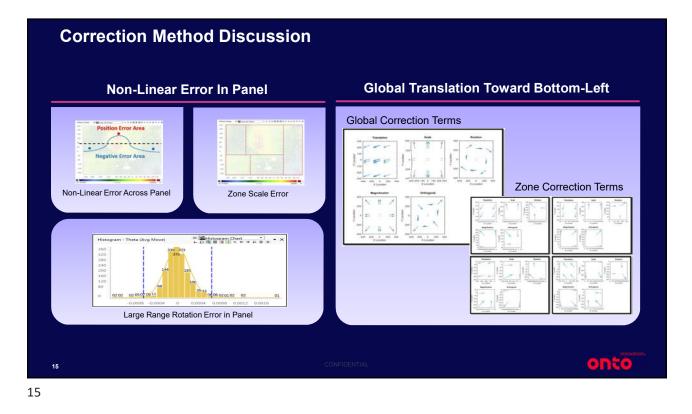

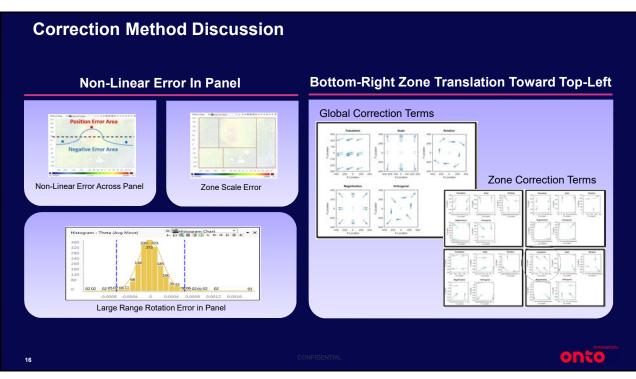

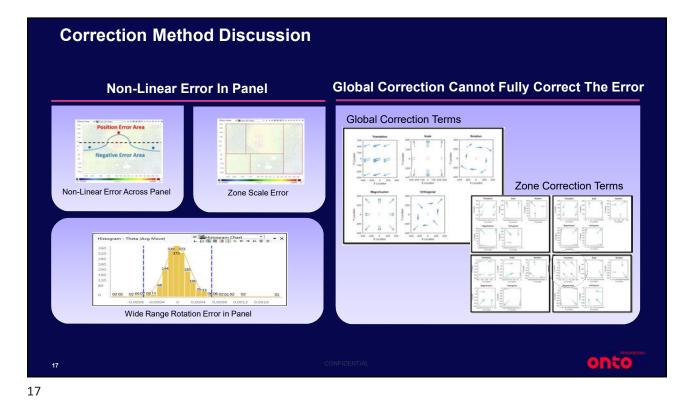

Challenge #2: Panel Distortion

#### JetStep® X500

• During panel processing, the continuous thermal cycling distorts the panel, which requires a lithography system to provide an alignment solution that delivers overlay performance that meets specification.

**Solution:** The JetStep X500 system utilizes a reticle chuck with 6 degrees of freedom, stage grid, and adjustable projection lens elements, to automatically provide an alignment solution that ensures high package yield.

#### COPPER CLAD LAMINATE (CCL ORGANIC SUBSTRATE

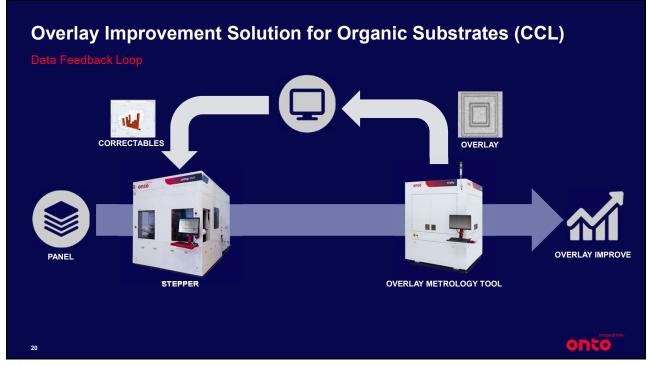

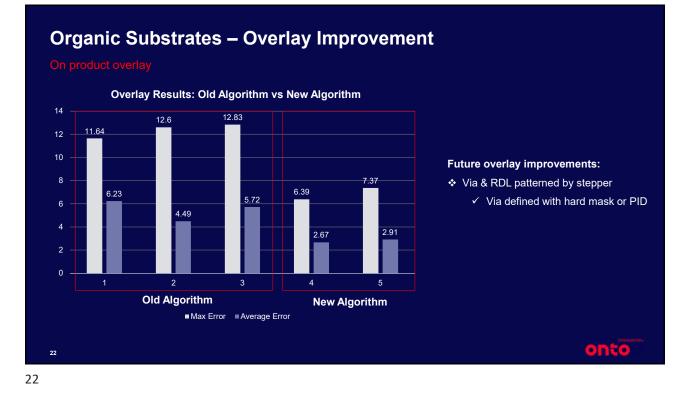

## **Overlay Improvement Solution for Organic Substrates (CCL)**

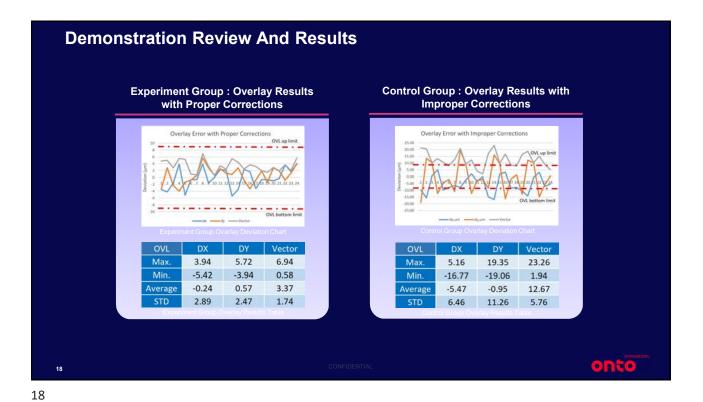

New algorithm to optimize on product overlay

## Packaging Applications Center of Excellence (PACE)

#### Leadership through R&D

Vision: Establish Onto as the Innovation Leader in Advanced Packaging

Mission: Accelerate the Advanced Packaging Technology Roadmap by working with customers, material suppliers, and OEMs to create and demonstrate next generation hardware and software solutions for the PLP market

onto

**Abstract:** "As the Advanced Packaging substrate interconnect density continues to increase rapidly, driven by next generation HPC, AI and VR/AR applications, there has been a paradigm shift in the package architecture to replace organic substrates with glass core substrates. Typically, organic substrates support HVM RDL structures of 9/12 µm line/space and, in R&D, down to 5/5 µm line/space. Beyond this, the substrate's dimensional stability and flatness will limit the resolution and overlay performance, impacting customer product roadmaps. Glass core substrates are expected to provide the solution. However, glass core has its own challenges. Onto Innovation understands these challenges, and provides solutions through its lithography, inspection, metrology and SW products. Onto Innovation is working with adjacent OEMs and the material supply chain to provide customers with early access to next generation products through its Packaging Applications Center of Excellence (PACE). This talk will discuss the benefits and challenges of both architectures and explores the possibility of extending the useful life of organic substrates beyond 5/5 µm line/space.

25